5.7 KiB

| title | description | date |

|---|---|---|

| yosys4gal: a Yosys Synthesis flow for GAL chips | Bringing modern synthesis to 30-year old technology with Yosys and Rust. | 2024-06-14 |

A history lesson

During the semiconductor revolution, a dilemma appeared: Designing new ICs required a lot of time and effort to create the mask, and iteration was expensive. At the time, IC designs were very simple, since the available tools/compute to do tasks like optimization or place-and-route were limited. And what if you wanted a low-volume design? Programmable Logic Arrays (PLAs) were an early approach to these problems. The idea was simple: create a flexible logic architecture that could be modified later in the process to implement various digital designs. These worked by using matrices of wires in a Sum-of-Products architecture. Inputs would be fed with their normal and inverted forms to a bank of AND gates, which would select various inputs using a fuse tie on the die and create product terms. The outputs of the AND gates would then be fed into OR gates, which would create the sum term for the whole output.

This design was popular, since it allowed for less-certain aspects of the chip to be moved to a later design process. Eventually, hardware people got jealous of the fast (for the time) compile-evaluate loops in software, and so PAL (Programmable Array Logic) was invented. These are similar to PLA logic, but the fuses are programmed using a simple programmer rather than a complex die process. This means that a developer with a pile of chips can program one, test it, make some adjustments, and then program the next. Later versions would solve the whole one-time-programmable aspect using UV-erasable EEPROM.

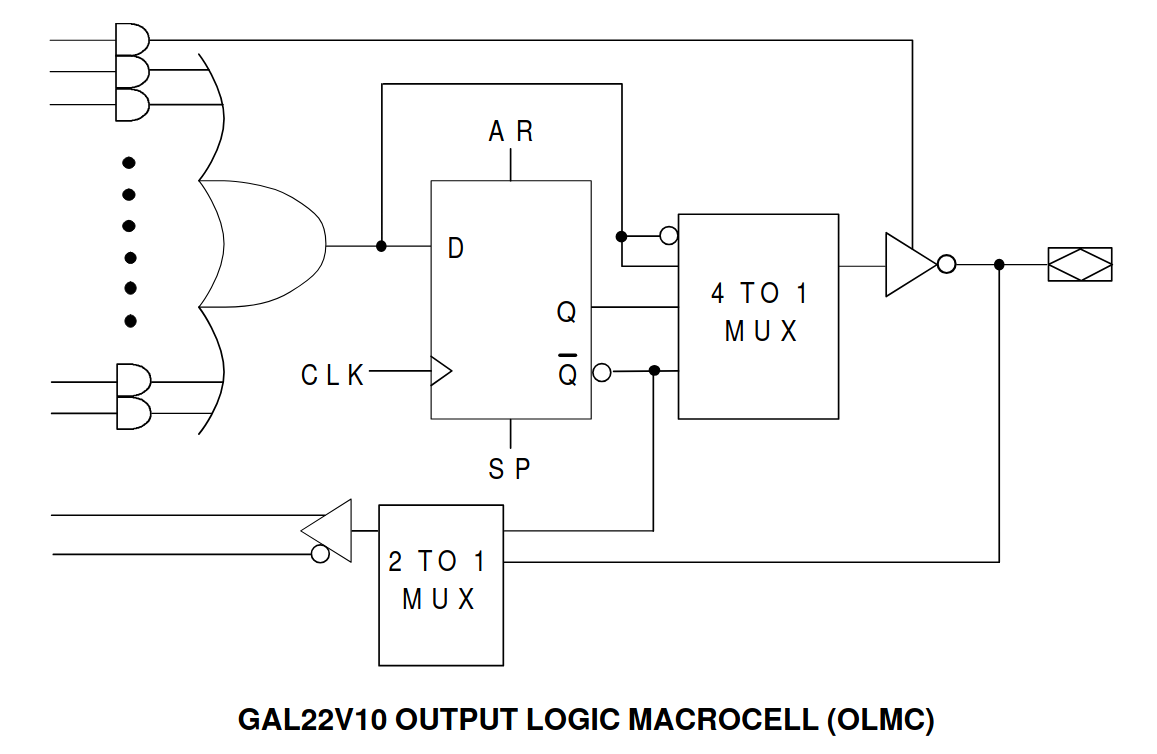

Demands would increase further and flip-flops would be added, as well as feedback capability. This allows for very complex functions to be implemented, since you can chain "rows" of the output blocks. This culminated in the GAL22V10, which was an electronically-erasable, 22-pin programmable logic block, which had up to 10 outputs that could be registered and used for feedback.

Back To Today: GALs in the 21st Century

These days, modern FPGA technology can be yours for a couple of bucks. Open-source toolchains allow fast, easy development, and the glut of Verilog resources online makes it easier than ever to enter the world of hardware design. But there are times when GALs might still be useful. For one, they start up instantly. Some FPGAs have a very fast one-time- programmable internal ROM, but this loses the "field-programmable" aspect which makes FPGAs desirable. In most cases the bitstream must be loaded from an external SPI flash. This can take up to a few seconds, which may not be acceptable if the logic is critical. Another important factor is the chip packaging. Most FPGAs are BGA packages, with some offering QFN or even a few QFP variants, but none are available in any DIP form factor, at least without a small board in between. The ATF22V10 (which is a clone/successor of the GAL22V10) is available in DIP, SSOP, and even PLCC if that's your jam. The package options make GALs perfect for breadboard applications. You could use it like an 8-in-1 74-series logic chip, changing the function depending on what you need. Additionally, GALs operate at 5 volts is useful when interfacing with older systems and removes the need for a level shifter.

However, this isn't all great. Programming GALs is an exercise in frustration. Take a look at a basic combinatorial assembly file:

GAL16V8

CombTest

Clock I0 I1 I2 I3 I4 I5 NC NC GND

/OE O0 O1 O2 O3 O4 I6 NC NC VCC

O0 = I0 * I1

O1 = I2 + I3 + I6

O2 = I4 * /I5 + /I4 * I5

O3 = I0 * I1 * I2 * I3 * I4 * I5

/O4 = I0 + I1 + I2 + I3 + I4 + I5

DESCRIPTION

Simple test of combinatorial logic.

In the contrived example the behavior is pretty clear, but it's not exactly a stellar format for writing complex logic. Plus, there's no way to integrate or test this in a larger system (we'll get back to this). Compared to the Verilog flow, with simulation, testbenches, and synthesis, the raw assembly is stuck in the 80s and requires manual logic simplification.

Verilog compilers for GALs did exist, but they ran on old-as-dirt systems, didn't have any significant optimization capabilities, and were almost always proprietary. What if we could make our own open-source Verilog flow for GAL chips? Then we could write test benches in Verilog, map complex designs onto the chip, and even integrate our designs with FPGAs later down the line.

The idea

GAL assembly is still common

Is this useful?

No, not really.

Well, there's a very very niche use case. These parts are 5-volt tolerant, and come in DIP packages. If you needed some basic glue logic when working on an older 5 volt system, you might want to have a few of these + a programmer instead of a collection of 74-series logic. At the very least, these chips can emulate any 74-series chip, and can reduce a multi-chip design to a single chip. The DIP form factor makes it much easier to breadboard, and the chips have zero start up delay.

In that narrow use case, yosys4gal is rather crucial. You no longer need WinCUPL or any old software, instead

using Verilog + Yosys. Your designs are automatically optimized, which makes it easier to fit more complex logic. And since it's verilog,

you can integrate it into a larger simulation or move it to an FPGA later if you desire.